# **Computer Hardware**

# **MJ Rutter**

mjr19@cam.ac.uk

Michaelmas 2013

©2013 MJ Rutter

# **Computer Hardware**

MJ Rutter mjr19@cam

Michaelmas 2013

# Bibliography

*Computer Architecture, A Qualitative Approach, 5th Ed.*, Hennessy, JL and Patterson, DA, pub. Morgan Kaufmann, c.£40.

Usually considered the standard textbook on computer architecture, and kept reasonably upto-date. The fifth edition was published in 2011, although much material in earlier editions is still relevant, and early editions have more on paper, and less on CD / online, though with 850 pages, there is quite a lot on paper...

# Contents

| History                               |

|---------------------------------------|

| The CPU 10                            |

| instructions                          |

| pipelines                             |

| vector computers                      |

| performance measures                  |

| Memory 44                             |

| DRAM                                  |

| caches                                |

| Memory Access Patterns in Practice 84 |

| matrix multiplication                 |

| matrix transposition                  |

| Memory Management 120                 |

| virtual addressing                    |

| paging to disk                        |

| memory segments                       |

| Hello: My First Program   160         |

| direct hardware access                |

| using the OS                          |

| using libraries                       |

| Compilers & Optimisation 19           |

| optimisation                    | . 197 |

|---------------------------------|-------|

| the pitfalls of F90             | . 221 |

| Disks, Filesystem & Fileservers | 234   |

| disks                           | . 235 |

| RAID                            | . 244 |

| filesystems                     | . 247 |

| fileservers                     | . 265 |

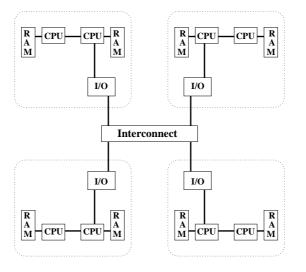

| Parallel Computers              | 274   |

| multitasking                    | . 274 |

| parallel computers              | . 278 |

| MPP                             | . 282 |

|                                 | 200   |

| SMP                             | . 289 |

| SMP                             |       |

# History

# History: to 1970

| 1951 | Ferranti Mk I: first commercial computer         |  |

|------|--------------------------------------------------|--|

|      | UNIVAC I: memory with parity                     |  |

| 1953 | EDSAC I 'heavily used' for science (Cambridge)   |  |

| 1954 | Fortran I (IBM)                                  |  |

| 1955 | Floating point in hardware (IBM 704)             |  |

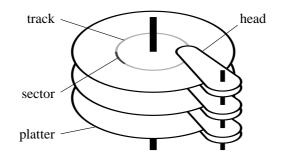

| 1956 | Hard disk drive prototype. $24''$ platters (IBM) |  |

| 1961 | Fortran IV                                       |  |

|      | Pipelined CPU (IBM 7030)                         |  |

| 1962 | Hard disk drive with flying heads (IBM)          |  |

| 1963 |                                                  |  |

|      | Virtual memory & paging (Ferranti Atlas)         |  |

| 1964 | First BASIC                                      |  |

| 1967 | ASCII character encoding (current version)       |  |

|      | GE635 / Multics: SMP (General Elect)             |  |

| 1968 | Cache in commercial computer (IBM 360/85)        |  |

|      | Mouse demonstrated                               |  |

|      | Reduce: computer algebra package                 |  |

| 1969 | ARPAnet: wide area network                       |  |

|      | Fully pipelined functional units (CDC 7600)      |  |

|      | Out of order execution (IBM 360/91)              |  |

|      |                                                  |  |

|      |                                                  |  |

| 1970 | First DRAM chip. 1Kbit. (Intel)              |  |  |

|------|----------------------------------------------|--|--|

|      | First floppy disk. 8" (IBM)                  |  |  |

| 1971 |                                              |  |  |

|      | Pascal                                       |  |  |

|      | First email                                  |  |  |

| 1972 | Fortran 66 standard published                |  |  |

|      | First vector computer (CDC)                  |  |  |

|      | First TLB (IBM 370)                          |  |  |

|      | ASC: computer with 'ECC' memory (TI)         |  |  |

| 1973 |                                              |  |  |

| 1974 |                                              |  |  |

| 1975 | UNIX appears outside AT&T                    |  |  |

|      | Ethernet appears (Xerox)                     |  |  |

| 1976 | Apple I launched. \$666.66                   |  |  |

|      | Cray I, ILLIAC IV                            |  |  |

|      | Z80 CPU (used in Sinclair ZX series) (Zilog) |  |  |

|      | $5\frac{1}{4}^{\prime\prime}$ floppy disk    |  |  |

| 1978 | K&R C appears (AT&T)                         |  |  |

|      | TCP/IP                                       |  |  |

|      | Intel 8086 processor                         |  |  |

|      | Laser printer (Xerox)                        |  |  |

|      | WordStar (early wordprocessor)               |  |  |

|      | First VAX (11/780) and VMS (DEC)             |  |  |

| 1979 | TEX                                          |  |  |

|      |                                              |  |  |

| 1980 | Sinclair ZX80 £100 ( $10^5$ sold eventually)        |

|------|-----------------------------------------------------|

|      | Fortran 77 standard published                       |

| 1981 | Sinclair ZX81 £70 ( $10^6$ sold eventually)         |

|      | $3\frac{1}{2}''$ floppy disk (Sony)                 |

|      | IBM PC & MS DOS version 1 \$3,285                   |

|      | SMTP (current email standard) proposed              |

| 1982 | Sinclair ZX Spectrum £175 48KB colour               |

|      | Acorn BBC model B £400 32KB colour                  |

|      | Commodore64 \$600 (10 <sup>7</sup> sold eventually) |

|      | Cray X-MP (first multiprocessor Cray)               |

|      | Motorola 68000 (commodity 32 bit CPU)               |

| 1983 | Internet defined to be TCP/IP only                  |

|      | Apple IIe \$1,400                                   |

|      | IBM XT, \$7,545                                     |

|      | Caltech Cosmic Cube: 64 node 8086/7 MPP             |

| 1984 | Apple Macintosh \$2,500. 128KB, 9" B&W screen       |

|      | Sinclair QL £400. 128KB                             |

|      | IBM AT, \$6,150. 256KB                              |

|      | CD ROM                                              |

| 1985 | LATEX2.09                                           |

|      | PostScript (Adobe)                                  |

|      | Ethernet formally standardised                      |

|      | IEEE 748 formally standardised                      |

|      | Intel i386 (Intel's first 32 bit CPU)               |

|      | X10R1 (forerunner of X11) (MIT)                     |

|      | C++                                                 |

# **History: the RISCs**

| 1986 | MIPS R2000, RISC CPU (used by SGI and DEC)       |  |

|------|--------------------------------------------------|--|

|      | SCSI formally standardised                       |  |

| 1987 | Intel i860 (Intel's first RISC CPU)              |  |

|      | Acorn Archimedes (ARM RISC) £800                 |  |

|      | SPARC I, RISC CPU (Sun)                          |  |

|      | Macintosh II \$4,000. FPU and colour.            |  |

|      | Multiflow Trace/200: VLIW CPU                    |  |

|      | X11R1 (MIT)                                      |  |

| 1989 | ANSI C                                           |  |

| 1990 | PostScript Level 2                               |  |

|      | Power I: superscalar RISC (IBM)                  |  |

|      | MS Windows 3.0                                   |  |

| 1991 | World Wide Web / HTTP                            |  |

|      | PVM (later superceded by MPI)                    |  |

|      | Fortran 90                                       |  |

| 1992 | PCI                                              |  |

|      | OpenGL                                           |  |

|      | OS/2 2.0 (32 bit a year before Windows NT) (IBM) |  |

|      | Alpha 21064: 64 bit superscalar RISC CPU (DEC)   |  |

|      |                                                  |  |

**A Summary of History**

The above timeline stops about two decades before a precursor to this talk was first given. Computing is not a fast-moving subject, and little of consequence has happened since...

By 1970 the concepts of disk drives, floating point, memory paging, parity protection, multitasking, caches, pipelining and out of order execution have all appeared in commercial systems, and high-level languages and wide area networking have been developed. The 1970s themselves add vector computers and error correcting memory, and implicit with the vector computers, RISC.

The rest is just enhanced technology rather than new concepts. The 1980s see the first serious parallel computers, and much marketing in a home computer boom. The slight novelty to arrive in the 21st century is the ability of graphics cards to do floating point arithmetic, and to run (increasingly complex) programs. ATI's 9700 (R300) launched in late 2002 supported FP arithmetic. Nvidia followed a few months later.

# The CPU

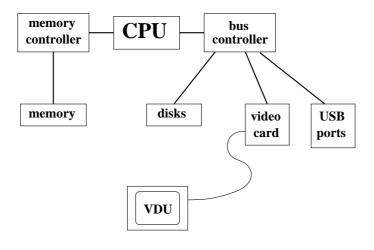

# Inside the Computer

# The Heart of the Computer

The CPU, which for the moment we assume has a single core, is the brains of the computer. Everything else is subordinate to this source of intellect.

A typical modern CPU understands two main classes of data: integer and floating point. Within those classes it may understand some additional subclasses, such as different precisions.

It can perform basic arithmetic operations and comparisons, governed by a sequence of instructions, or *program*.

It can also perform comparisons, the result of which can change the *execution path* through the program.

Its sole language is machine code, and each family of processors speaks a completely different variant of machine code.

#### Schematic of Typical RISC CPU

#### What the bits do

- Memory: not part of the CPU. Used to store both program and data.

- Instruction fetcher: fetches next machine code instruction from memory.

- Instruction decoder: decodes instruction, and sends relevant data on to...

- Functional unit: dedicated to performing a single operation

- Registers: store the input and output of the functional units There are typically about 32 floating point registers, and 32 integer registers.

Partly for historical reasons, there is a separation between the integer and floating point parts of the CPU.

On some CPUs the separation is so strong that the only way of transferring data between the integer and floating point registers is via the memory. On some older CPUs (e.g. the Intel 386), the FPU (floating point unit) is optional and physically distinct.

# **Clock Watching**

The best known part of a CPU is probably the *clock*. The clock is simply an external signal used for synchronisation. It is a square wave running at a particular frequency.

Clocks are used within the CPU to keep the various parts synchronised, and also on the data paths between different components external to the CPU. Such data paths are called *buses*, and are characterised by a *width* (the number of wires (i.e. bits) in parallel) as well as a clock speed. External buses are usually narrower and slower than ones internal to the CPU.

Although sychronisation is important – every good orchestra needs a good conductor – it is a means not an end. A CPU may be designed to do a lot of work in one clock cycle, or very little, and comparing clock rates between different CPU designs is meaningless.

The bandwidth of a bus is simple its width  $\times$  its clock speed  $\times$  the number of data transfers per clock cycle. For the original IBM PC bus, 1 byte  $\times$  4.77MHz  $\times$  one quarter (1.2MB/s). For PCIe v2 x16, 2 bytes  $\times$  5GHz  $\times$  four fifths (8GB/s).

#### Work Done per Clock Cycle

Intel's 'Sandy Bridge' and 'Ivy Bridge' range of CPUs can theoretically sustain four floating point adds and four floating point multiplies per core per clock-cycle.

The previous generations (Nehalem and Core2) just two adds and two multiplies.

The previous generation (Pentium4) just one add and one multiply.

The previous generations (Pentium to Pentium III) just one add or multiply.

The previous generation (i486), about a dozen clock cycles for one FP add or multiply. The generation before (i386/i387) about two dozen cycles.

Since the late 1980s clock speeds have improved by a factor of about 100 (c. 30MHz to c. 3GHz). The amount of floating point work a single core can do in one clock cycle has also increased by a factor of about 100.

# **Typical instructions**

#### **Integer:**

- arithmetic:  $+, -, \times, /$ , negate

- logical: and, or, not, xor

- bitwise: shift, rotate

- comparison

- load / store (copy between register and memory)

#### **Floating point:**

- arithmetic:  $+, -, \times, /, \sqrt{}$ , negate, modulus

- convert to / from integer

- comparison

- load / store (copy between register and memory)

#### **Control:**

• (conditional) branch (i.e. goto)

# A typical instruction

fadd f4,f5,f6

add the contents of floating point registers 4 and 5, placing the result in register 6.

Execution sequence:

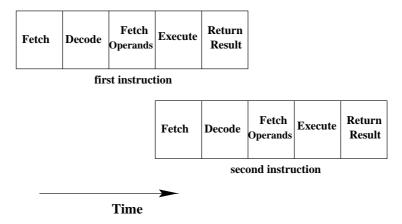

- fetch instruction from memory

- decode it

- collect required data (f4 and f5) and send to floating point addition unit

- wait for add to complete

- retrieve result and place in f6

Exact details vary from processor to processor.

Always a *pipeline* of operations which must be performed sequentially.

The number of *stages* in the pipeline, or *pipeline depth*, can be between about 5 and 15 depending on the processor.

18

# Making it go faster...

If each pipeline stage takes a single clock-cycle to complete, the previous scheme would suggest that it takes five clock cycles to execute a single instruction.

Clearly one can do better: in the absence of branch instructions, the next instruction can always be both fetched and decoded whilst the previous instruction is executing. This shortens our example to three clock cycles per instruction.

#### ... and faster...

A functional unit may itself be pipelined. Considering again floating-point addition, even in base 10 there are three distinct stages to perform:

$9.67 \times 10^5 + 4 \times 10^4$

First the exponents are adjusted so that they are equal:

$9.67 \times 10^5 + 0.4 \times 10^5$

only then can the mantissas be added:  $10.07 \times 10^5$

then one may have to readjust the exponent:  $1.007\times 10^6$

So floating point addition usually takes at least three clock cycles in the execution stage. But the adder may be able to start a new addition ever clock cycle, as these stages use distinct parts of the adder.

Such an adder would have a *latency* of three clock cycles, but a *repeat* or *issue rate* of one clock cycle.

20

#### ...and faster...

Further improvements are governed by data dependency. Consider:

fadd f4,f5,f6 fmul f6,f7,f4

(Add f4 and f5 placing the result in f6, then multiply f6 and f7 placing the result back in f4.)

Clearly the add must finish (f6 must be calculated) before the multiply can start. There is a data dependency between the multiply and the add.

But consider

fadd f4,f5,f6 fmul f3,f7,f9

Now any degree of overlap between these two instructions is permissible: they could even execute simultaneously or in the reverse order and still give the same result.

#### ...and faster

We have now reached one instruction per cycle, assuming data independency.

If the instructions are short and simple, it is easy for the CPU to dispatch multiple instructions simultaneously, provided that each functional unit receives no more than one instruction per clock cycle.

So, in theory, an FP add, an FP multiply, an integer add, an FP load and an integer store might all be started simultaneously.

RISC instruction sets are carefully designed so that each instruction uses only one functional unit, and it is easy for the decode/issue logic to spot dependencies. CISC is a mess, with a single instruction potentially using several functional units.

RISC (Reduced Instruction Set Computer) relies on the instructions being very simple – the above CISC example would certainly be three RISC instructions – and then letting the CPU overlap them as much as possible.

22

#### **Breaking Dependencies**

| for(i=0;i <n;i++){< th=""><th>do i=1,n</th></n;i++){<> | do i=1,n     |

|--------------------------------------------------------|--------------|

| sum+=a[i];                                             | sum=sum+a(i) |

| }                                                      | enddo        |

This would appear to require three clock cycles per iteration, as the iteration sum=sum+a[i+1] cannot start until sum=sum+a[i] has completed. However, consider

| for(i=0;i <n;i+=3){< th=""><th>do i=1,n,3</th></n;i+=3){<> | do i=1,n,3   |

|------------------------------------------------------------|--------------|

| s1+=a[i];                                                  | s1=s1+a(i)   |

| s2+=a[i+1];                                                | s2=s2+a(i+1) |

| s3+=a[i+2];                                                | s3=s3+a(i+2) |

| }                                                          | enddo        |

| sum=s1+s2+s3;                                              | sum=s1+s2+s3 |

The three distinct partial sums have no interdependency, so one add can be issued every cycle.

**Do not** do this by hand. This is a job for an optimising compiler, as you need to know a lot about the particular processor you are using before you can tell how many paritial sums to use. And worrying about *codas* for n not divisible by 3 is tedious.

CISC (Complex Instruction Set Computer) relies on a single instruction doing a lot of work: maybe incrementing a pointer and loading data from memory and doing an arithmetic operation.

#### **An Aside: Choices and Families**

There are many choices to make in CPU design. Fixed length instructions, or variable? How many integer registers? How big? How many floating point registers (if any)? Should 'complicated' operations be supported? (Division, square roots, trig. functions, ...). Should functional units have direct access to memory? Should instructions overwrite an argument with the result? Etc.

This has led to many different CPU families, with no compatibility existing between families, but backwards compatibility within families (newer members can run code compiled for older members).

In the past different families were common in desktop computers. Now the Intel/AMD family has a near monopoly here, but mobile phones usually contain ARM-based CPUs, and printers, routers, cameras etc., often contain MIPS-based CPUs. The Sony PlayStation uses CPUs derived from IBM's Power range, as do the Nintendo Wii and Microsoft Xbox.

#### Compilers

CPUs from different families will speak rather different languages, and, even within a family, new instructions get added from generation to generation to make use of new features.

Hence intelligent Humans write code in well-defined processor-independent languages, such as Fortran or C, and let the compiler do the work of producing the correct instructions for a given CPU. The compiler must also worry quite a lot about interfacing to a given operating system, so running a Windows executable on a machine running MacOS or Linux, even if they have the same CPU, is far from trivial (and generally impossible).

Compilers can, and do, of course, differ in how fast the sequence of instructions they translate code into runs, and even how accurate the translation is.

At the other end of the computing scale, Intel/AMD has only recently begun to dominate. However, the top twenty machines in the November 2010 Top500 supercomputer list include three using the IBM Power series of processors, and another three using GPUs to assist performance. Back in June 2000, the Top500 list included a single Intel entry, admittedly top, the very specialised one-off ASCI Red. By June 2005 Intel's position had improved to 7 in the top 20.

Well-defined processor-independent languages tend to be supported on by a wide variety of platforms over a long period of time. What I wrote a *long* time ago in Fortran 77 or ANSI C I can still run easily today. What I wrote in QuickBASIC then rewrote in TurboBASIC is now useless again, and became useless remarkably quickly.

# **Ignoring Intel**

Despite Intel's desktop dominance, this course is utterly biased towards discussing RISC machines. It is not fun to explain an instruction such as faddl (%ecx, %eax, 8)

(add to the register at the top of the FP register stack the value found at the memory address given by the ecx register plus  $8 \times$  the eax register) which uses an integer shift ( $\times 8$ ), integer add, FP load and FP add in one instruction.

Furthermore, since the days of the Pentium Pro (1995), Intel's processors have had RISC cores, and a CISC to RISC translator feeding instructions to the core. The RISC core is never exposed to the programmer, leaving Intel free to change it dramatically between processors. A hideous operation like the above will be broken into three or four " $\mu$ -ops" for the core. A simpler CISC instruction might map to single  $\mu$ -op (micro-op).

Designing a CISC core to do a decent degree of pipelining and simultaneous execution, when instructions may use multiple functional units, and memory operations are not neatly separated, is more painful than doing runtime CISC to RISC conversion.

26

# A Branch in the Pipe

So far we have assumed a linear sequence of instructions. What happens if there is a branch?

```

double t=0.0; int i,n;

t=0

for (i=0;i<n;i++) t=t+x[i];</pre>

do i=1, n

t=t+x(i)

# $17 contains n, # $16 contains x

enddo

fclr $f0

clr $1

ble $17,L$5

L$6:

ldt

$f1, ($16)

addl $1, 1, $1

cmplt $1, $17, $3

lda $16, 8($16)

addt $f0, $f1, $f0

$3, L$6

bne

L$5:

```

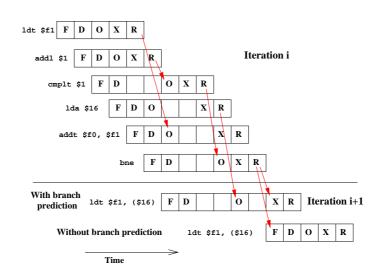

There will be a conditional jump or *branch* at the end of the loop. If the processor simply fetches and decodes the instructions following the branch, then when the branch is taken, the pipeline is suddenly empty.

#### **Assembler in More Detail**

The above is Alpha assembler. The integer registers \$1, \$3, \$16 and \$17 are used, and the floating point registers \$f0 and \$f1. The instructions are of the form 'op a,b,c' meaning 'c=a op b'.

| fclr \$f0<br>clr \$1  | Float CLeaR \$f0 – place zero in \$f0<br>CLeaR \$1              |

|-----------------------|-----------------------------------------------------------------|

| ble \$17, L\$5        | Branch if Less than or Equal on comparing \$17                  |

|                       | to (an implicit) zero and jump to L\$5 if less (i.e. skip loop) |

| L\$6:                 |                                                                 |

| ldt \$f1, (\$16)      | LoaD \$f1 with value value from                                 |

|                       | memory from address \$16                                        |

| addl \$1, 1, \$1      | \$1=\$1+1                                                       |

| cmplt \$1, \$17, \$3  | CoMPare \$1 to \$17 and place result in \$3                     |

| lda \$16, 8(\$16)     | LoaD Address, effectively \$16=\$16+8                           |

| addt \$f0, \$f1, \$f0 | \$f0=\$f0+\$f1                                                  |

| bne \$3,L\$6          | Branch Not Equal – if counter $\neq$ n, do another iteration    |

| L\$5:                 |                                                                 |

The above is only assembler anyway, readable by Humans. The machine-code instructions that the CPU actually interprets have a simple mapping from assembler, but will be different again. For the Alpha, each machine code instruction is four bytes long. For IA32 machines, between one and a dozen or so bytes.

28

#### **Predictions**

With the simplistic pipeline model of page 19, the loop will take 9 clock cycles per iteration if the CPU predicts the branch and fetches the next instruction appropriately. With no prediction, it will take 12 cycles.

A 'real' CPU has a pipeline *depth* much greater than the five slots shown here: usually ten to twenty. The penalty for a mispredicted branch is therefore large.

Note the *stalls* in the pipeline based on data dependencies (shown with red arrows) or to prevent the execution order changing. If the instruction fetch unit fetches one instruction per cycle, stalls will cause a build-up in the number of *in flight* instructions. Eventually the fetcher will pause to allow things to quieten down.

#### **Speculation**

In the above example, the CPU does not begin to execute the instruction after the branch until it knows whether the branch was taken: it merely fetches and decodes it, and collects its operands. A further level of sophistication allows the CPU to execute the next instruction(s), provided it is able to throw away all results and side-effects if the branch was mispredicted.

Such execution is called *speculative execution*. In the above example, it would enable the ldt to finish one cycle earlier, progressing to the point of writing to the register before the result of the branch were known.

More advanced forms of speculation would permit the write to the register to proceed, and would undo the write should the branch have been mispredicted.

Errors caused by speculated instructions must be carefully discarded. It is no use if if (x>0) = sqrt(x); causes a crash when the square root is executed speculatively with x=-1, nor if if (i<1000) = x=a[i]; causes a crash when i=2000 due to trying to access a[2000].

Almost all current processors are capable of some degree of speculation.

ldt \$f1 F D O X R Iteration i addl \$1 F D O X cmplt \$1 F D O X R lda \$16 F D O X R addt \$f0, \$f1 D 0 Х O X R F D F D O X R Iteration i+1 ldt \$f1, (\$16) Time

#### Previously the cmplt is delayed due to a dependency on the addl immediately preceeding it. However, the next instruction has no relevant dependencies. A processor capable of *out-of-order* execution could execute the lda before the cmplt.

The timing above assumes that the ldt of the next iteration can be executed speculatively and OOO before the branch. Different CPUs are capable of differing amounts of speculation and OOOE.

The EV6 Alpha does OOOE, the EV5 does not, nor does the UltraSPARC III. In this simple case, the compiler erred in not changing the order itself. However, the compiler was told not to optimise for this example.

#### 000!

| Instruction   | Latency | Issue rate |

|---------------|---------|------------|

| iadd/isub     | 1       | 1          |

| and, or, etc. | 1       | 1          |

| shift, rotate | 1       | 1          |

| load/store    | 1-2     | 1          |

| imul          | 3-15    | 3-15       |

| fadd          | 3       | 1          |

| fmul          | 2-3     | 1          |

| fdiv/fsqrt    | 15-25   | 15-25      |

#### **Typical functional unit speeds**

In general, most things 1 to 3 clock cycles and pipelined, except integer  $\times$  and  $\div$ , and floating point  $\div$  and  $\sqrt{}$ .

'Typical' for simple RISC processors. Some processors tend to have longer fp latencies: 4 for fadd and fmul for the UltraSPARC III, 5 and 7 respectively for the Pentium 4, 3 and 5 respectively for the Core 2 / Nehalem / Sandy Bridge.

32

#### **Floating Point Rules?**

Those slow integer multiplies are more common that it would seem at first. Consider:

```

double precision x(1000), y(500, 500)

```

The address of x(i) is the address of x(1) plus  $8 \times (i - 1)$ . That multiplication is just a shift. However, y(i,j) is that of y(1,1) plus  $8 \times ((i - 1) + (j - 1) \times 500)$ . A lurking integer multiply!

Compilers may do quite a good job of eliminating unnecessary multiplies from common sequential access patterns.

C does things rather differently, but not necessarily better.

#### Hard or Soft?

The simple operations, such as +, - and \* are performed by dedicated pipelined pieces of hardware which typically produce one result each clock cycle, and take around four clock cycles to produce a given result.

Slightly more complicated operations, such as / and  $\sqrt{}$  may be done with *microcode*. Microcode is a tiny program on the CPU itself which is executed when a particular instruction, e.g. /, is received, and which may use the other hardware units on the CPU multiple times.

Yet more difficult operations, such as trig. functions or logs, are usually done entirely with software in a library. The library uses a collection of power series or rational approximations to the function, and the CPU needs evaluate only the basic arithmetic operations.

The IA32 range is unusual in having microcoded instructions for trig. functions and logs. Even on a Core2 or Core i7, a single trig instruction can take over 100 clock cycles to execute. RISC CPUs tend to avoid microcode on this scale.

The trig. function instructions date from the old era of the x87 maths coprocessor, and no corresponding instruction exists for data in the newer SSE2/XMM registers.

34

# **Division by Multiplication?**

There are many ways to perform floating point division. With a fast hardware multiplier, Newton-Raphson like iterative algorithms can be attractive.

$$x_{n+1} = 2x_n - bx_n^2$$

will, for reasonable starting guesses, converge to 1/b. E.g., with b = 6.

- $n \quad x_n$

- 0 0.2

- 1 0.16

- 2 0.1664

- 3 0.16666624

- 4 0.166666666655744

How does one form an initial guess? Remember that the number is already stored as  $m \times 2^e$ , and  $0.5 \le m < 1$ . So a guess of  $0.75 \times 2^{1-e}$  is within a factor of 1.5. In practice the first few bits of m are used to index a lookup table to provide the initial guess of the mantissa.

A similar scheme enables one to find  $1/\sqrt{b}$ , and then  $\sqrt{b} = b \times 1/\sqrt{b}$ , using the recurrance  $x \to 0.5x(3 - bx^2)$

#### **Vector Computers**

The phrase 'vector computer' means different things to different people.

To Cray, it meant having special 'vector' registers which store multiple floating point numbers, 'multiple' generally being 64, and on some models 128. These registers could be operated on using single instructions, which would perform element-wise operations on the whole register. Usually there would be just a single addition unit, but a vadd instruction would take around 70 clock cycles – one cycle per element, and a small pipeline start overhead.

So the idea was that the vector registers gave a simple mechanism for presenting a long sequence of independent operations to a highly pipelined functional unit.

36

#### **Cray's Other Idea**

The other trick with vector Crays was to omit all data caches. Instead they employed a large number of banks of memory (typically sixteen), and used no-expense-spared SRAM for their main memory anyway. This gave them huge memory bandwidth. The Cray Y/MP-8, first sold in 1988, had a peak theoretical speed of 2.7 GFLOPS, about half that of a 2.8GHz Pentium 4 (introduced 2002). However, its memory bandwidth of around 27GB/s was considerably better than the P4 at under 4GB/s, and would still beat a single-socket Ivy Bridge machine (introduced 2012).

Not only was the Cray's ratio of memory bandwidth to floating point performance about fifty times higher than a current desktop, but its memory latency was low – lower than that of a current desktop machine – despite its clock speed being only 167MHz. The memory controller on the Cray could handle many outstanding memory requests, which further hid latencies. Of course, memory requests were likely to be generated 64 words at a time.

The weak spot of this system was dealing with strides which contained a large power of two. A stride of 16 doubles might cause all requests to go to a single memory bank, reducing performance by at least a factor of ten.

# **Intel and Vectorisation**

Intel's approach to vectorisation is very different from Cray's. The memory architecture is unchanged. The vector length is two or four (eight for the Xeon Phi), not sixty four.

But, Intel provides sufficient functional units, as putting extra transistors on a chip is now cheap, to operate on a whole vector at once. The vectorisation is used to keep multiple functional units busy at once, not in order to make efficient use of the pipeline in a single functional unit.

A Cray will run reasonably fast streaming huge arrays from main memory, with 10 bytes of memory bandwidth per peak FLOPS. An Intel processor, with around 0.2 bytes of memory bandwidth, won't. One needs to worry about its caches to get decent performance.

#### **Meaningless Indicators of Performance**

The only relevant performance indicator is how long a computer takes to run *your* code. Thus my fastest computer is not necessarily your fastest computer.

Often one buys a computer before one writes the code it has been bought for, so other 'real-world' metrics are useful. Some are not useful:

- MHz: the silliest: some CPUs take 4 clock cycles to perform one operation, others perform four operations in one clock cycle. Only any use when comparing otherwise identical CPUs.

- MIPS: Millions of Instructions Per Second. Theoretical peak speed of decode/issue logic, or maybe the time taken to run a 1970's benchmark. Gave rise to the name Meaningless Indicator of Performance.

- FLOPS: Floating Point Operations Per Second. Theoretical peak issue rate for floating point computational instructions, ignoring loads and stores and with optimal ratio of + to \*. Hence MFLOPS, GFLOPS, TFLOPS: 10<sup>6</sup>, 10<sup>9</sup>, 10<sup>12</sup> FLOPS.

# The Guilty Candidates: Linpack

#### Linpack 100x100

Solve 100x100 set of double precision linear equations using fixed FORTRAN source. Pity it takes just 0.7 s at 1 MFLOPS and uses under 100KB of memory. Only relevant for pocket calculators.

#### Linpack 1000x1000 or nxn

Solve  $1000 \times 1000$  (or  $n \times n$ ) set of double precision linear equations by any means. Usually coded using a blocking method, often in assembler. Is that relevant to your style of coding? Achieving less than 50% of a processor's theoretical peak performance is unusual.

Linpack is convenient in that it has an equal number of adds and multiplies uniformly distributed throughout the code. Thus a CPU with an equal number of FP adders and multipliers, and the ability to issue instructions to all simultaneously, can keep all busy.

40

#### **SPEC**

SPEC is a non-profit benchmarking organisation. It has two CPU benchmarking suites, one concentrating on integer performance, and one on floating point. Each consists of around ten programs, and the mean performance is reported.

Unfortunately, the benchmark suites need constant revision to keep ahead of CPU developments. The first was released in 1989, the second in 1992, the third in 1995. None of these use more than 8MB of data, so fit in cache with many current computers. Hence a fourth suite was released in 2000, and then another in 2006.

It is not possible to compare results from one suite with those from another, and the source is not publically available.

Number of operations:  $O(n^3)$ , memory usage  $O(n^2)$ . *n* chosen by manufacturer to maximise performance, which is reported in GFLOPS.

Until 2000, the floating point suite was entirely Fortran.

Two scores are reported, 'base', which permits two optimisation flags to the compiler, and 'peak' which allows any number of compiler flags. Changing the code is not permitted.

#### **SPEC** rates

SPEC also has a set of throughput benchmarks, which consist of running multiple copies of their serial benchmarks simultaneously. For multicore machines, this should work well, only in practice the cores compete for limited memory bandwidth, and it works less well than one might hope.

For instance, in late 2008 Intel published a result of 155 for a 24 core X7460 system. This essentially has four six-core Core 2 processors running at 2.66GHz. Clearly much faster than a single dual-core Core 2 processor at the same clock speed. However, the Core 2 E8200 achieved a score of 28.9 on this benchmark over six months earlier, so twelve times the core count has resulted in less than six times the throughput running serial codes.

At that time, AMD was easily beating Intel with four-socket machines. With four quad-core Opterons running at just 2.3GHz it could match the performance of the 24 core Intel machine, and at 2.7GHz it could achieve just over 200.

42

# Your Benchmark or Mine?

Picking the oldest desktop in TCM, a 2.67GHz Pentium 4, and the newest, a 3.1GHz quad core 'Haswell' CPU, I ran two benchmarks.

Linpack gave results of 3.88 GFLOPS for the P4, and 135 GFLOPS for the Haswell, a win for the Haswell by a factor of around 35.

A nasty synthetic integer benchmark I wrote gave run-times of 6.0s on the P4, and 9.7s on the Haswell, a win for the P4 by a factor of 1.6 in speed.

(Linux's notoriously meaningless 'BogoMIPS' benchmark is slightly kinder to the Haswell, giving it a score of 6,185 against 5,350 for the P4.)

It is all too easy for a vendor to use the benchmark of his choice to prove that his computer is faster than a given competitor.

The P4 was a 'Northwood' P4 first sold in 2002, the Haswell was first sold in 2013.

Intel has since caught up with AMD, and by early 2011 Intel could manage a score of 1150 using eight 8-core Xeon X7560s at 2.27GHz, whereas AMD scored 1310 with eight 12-core Opterons at 2.5GHz. The biggest machine to run this benchmark was an IBM with 32 8-core Power7 processors running at 4GHz, which scored 10,500.

# Memory

- DRAM

- Parity and ECC

- Going faster: wide bursts

- Going faster: caches

44

#### **Memory Design**

The first DRAM cell requiring just one transistor and one capacitor to store one bit was invented and produced by Intel in 1974. It was mostly responsible for the early importance of Intel as a chip manufacturer.

The design of DRAM has changed little. The speed, as we shall soon see, has changed little. The price has changed enormously. I can remember when memory cost around £1 per KB (early 1980s). It now costs around 1p per MB, a change of a factor of  $10^5$ , or a little more in real terms. This change in price has allowed a dramatic change in the amount of memory which a computer typically has.

Alternatives to DRAM are SRAM – very fast, but needs six transitors per bit, and flash RAM – unique in retaining data in the absence of power, but writes are slow *and* cause significant wear.

RAM: Random Access Memory - i.e. not block access (disk drive), nor sequential access (tape drive).

#### **D-RAM**

The charge in a DRAM cell slowly leaks away. So each cell is read, and then written back to, several times a second by *refresh* circuitary to keep the contents stable. This is why this type of memory is called Dynamic RAM.

Of course, as anyone in the HEP community can testify, one can charge lots of small capacitors, monitor their charge, and a sudden change means an ionisation event has occured in their dielectric – an energetic particle has been detected. DRAM is worrying similar to a semiconductor particle detector, so cautious people use extra DRAM cells to store an error correction / detection code so that stray cosmic rays do not end up in one's results. Such memory is called ECC memory. (Error Correcting Code.)

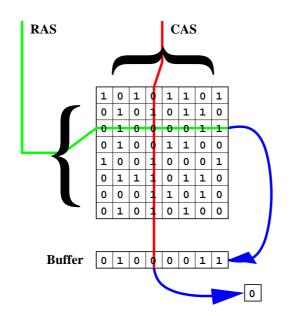

**DRAM** in Detail

# DRAM cells are arranged in (near-)square arrays. To read, first a row is selected and copied to a buffer, from which a column is selected, and the resulting single bit becomes the output. This example is a 64 bit DRAM.

This chip would need 3 *address lines* (i.e. pins) allowing 3 bits of address data to be presented at once, and a single data line. Also two pins for power, two for CAS and RAS, and one to indicate whether a read or a write is required.

Of course a 'real' DRAM chip would contain several tens of million bits.

#### **DRAM Read Timings**

To read a single bit from a DRAM chip, the following sequence takes place:

- Row placed on address lines, and Row Access Strobe pin signalled.

- After a suitable delay, column placed on address lines, and Column Access Strobe pin signalled.

- After another delay the one bit is ready for collection.

- The DRAM chip will automatically write the row back again, and will not accept a new row address until it has done so.

The same address lines are used for both the row and column access. This halves the number of addess lines needed, and adds the RAS and CAS pins.

Reading a DRAM cell causes a significant drain in the charge on its capacitor, so it needs to be refreshed before being read again.

# More Speed!

The above procedure is tediously slow. However, for reading consecutive addresses, one important improvement can be made.

Having copied a whole row into the buffer (which is usually SRAM (see later)), if another bit from the same row is required, simply changing the column address whilst signalling the CAS pin is sufficient. There is no need to wait for the chip to write the row back, and then to rerequest the same row. Thus Fast Page Mode (FPM) and Extended Data Out (EDO) DRAM.

Today's SDRAM (Synchronous DRAM) takes this approach one stage further. It assumes that the next (several) bits are wanted, and sends them in sequence without waiting to receive requests for their column addresses.

# Speed

Old-style memory quoted latencies which were simply the time it would take an idle chip to respond to a memory request. In the early 1980s this was about 250ns. By the early 1990s it was about 80ns.

Today timings are quoted as clock cycles for column access to data out ( $T_{CL}$  or  $T_{CAS}$ ) and idle to row select finished ( $T_{RCD}$ ) These are the first two numbers of the four usually quoted for memory timings. The clock refered to is the undoubled data clock, so a DDR3-1333 module with timings of 7-7-7-24 has a latency of 14 cycles of a 667MHz clock, or 21ns.

So in twenty years memory has got four times faster in terms of latency.

50

# Bandwidth

Bandwidth has improved much more over the same period. In the early 1980s memory was usually arranged to deliver 8 bits (one byte) at once, with eight chips working in parallel. By the early 1990s that had risen to 32 bits (4 bytes), and today one expects 128 bits (16 bytes) on any desktop.

More dramatic is the change in time taken to access consecutive items. In the 1980s the next item (whatever it was) took slightly longer to access, for the DRAM chip needed time to recover from the previous operation. So late 1980s 32 bit wide 80ns memory was unlikely to deliver as much as four bytes every 100ns, or 40MB/s. Now sequential access is anticipated, and arrives at the doubled clock speed, so at 1333MHz for DDR3-1333 memory. Coupled with being arranged with 128 bits in parallel, this leads to a theoretical bandwidth of 20GB/s.

So in twenty years the bandwidth has improved by a factor of about 500.

#### Parity

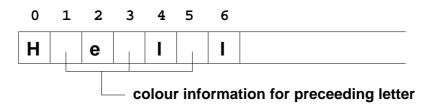

In the 1980s, business computers had memory arranged in bytes, with one extra bit per byte which stored parity information. This is simply the sum of the other bits, modulo 2. If the parity bit disagreed with the contents of the other eight bits, then the memory had suffered physical corruption, and the computer would usually crash, which is considered better than calmly going on generating wrong answers.

Calculating the parity value is quite cheap in terms of speed and complexity, and the extra storage needed is only 12.5%. However parity will detect only an odd number of bit-flips in the data protected by each parity bit. If an even number change, it does not notice. And it can never correct.

#### ECC

Better than parity is ECC memory (Error Correcting Code), usually SEC-DED (Single Error Corrected, Double Error Detected).

One code for dealing with n bits requires an extra  $2 + \log_2 n$  check bits. Each code now usually protects eight bytes, 64 bits, for which  $2 + \log_2 64 = 8$  extra check bits are needed. Once more, 12.5% extra, or one extra bit per byte. The example shows an ECC code operating on 8 bits of data.

One check bit is a parity check of the other check bits (green, top right), else errors in the check bits are undetected and cause erroneous 'corrections'. The other four check bits (red column) store parity information for the data bits indicated. A failing data bit causes a unique pattern in these bits. This is not the precise code used, & fails to detect 2-bit errors, but it shows the general principle.

Computers with parity could detect one bit in error per byte. Today's usual ECC code can correct a one bit error per 8 bytes, and detect a two bit error per eight bytes. Look up Hamming Codes for more information.

#### **Causes and Prevelance of Errors**

In the past most DRAM errors have been blamed on cosmic rays, more recent research suggest that this is not so. A study of Google's servers over a 30 month period suggests that faulty chips are a greater problem. Cosmic rays would be uniformly distributed, but the errors were much more clustered.

About 30% of the servers had at least one correctable error per year, but the average number of correctable errors per machine year was over 22,000. The probability of a machine which had one error having another within a year was 93%. The uncorrectable error rate was 1.3% per machine year.

The numbers are skewed by the fact that once insulation fails so as to lock a bit to one (or zero), then, on average, half the accesses will result in errors. In practice insulation can partially fail, such that the data are usually correct, unless neighbouring bits, temperature, ..., conspire to cause trouble.

Uncorrectable errors were usually preceded by correctable ones: over 60% of uncorrectable errors had been preceded by a correctable error in the same DIMM in the same month, whereas a random DIMM has a less than 1% correctable error rate per month.

'DRAM Errors in the Wild: a Large-Scale Field Study', Schroeder et al.

54

#### **ECC: Do We Care?**

A typical home PC, run for a few hours each day, with only about half as much memory as those Google servers, is unlikely to see an error in its five year life. One has about a one in ten chance of being unlucky. When running a hundred machines 24/7, the chances of getting through a month, let alone a year, without a correctable error would seem to be low.

Intel's desktop i3/i5/i7 processors do not support ECC memory, whereas their server-class Xeon processors all do. Most major server manufacturers (HP, Dell, IBM, etc.) simply do not sell any servers without ECC. Indeed, most also support the more sophisticated 'Chipkill' correction which can cope with one whole chip failing on a bus of 128 data bits and 16 'parity' bits.

'Chipkill' is IBM's trademark for a technology which Intel calls Intel x4 SDDC (single device data correction). It starts by interleaving the bits to form four 36 bit words, each word having one bit from each chip, so a SEC-DED code is sufficient for each word.

I have an 'ECC only' policy for servers, both file servers and machines likely to run jobs. In my Group, this means every desktop machine. The idea of doing financial calculations on a machine without ECC I find amusing and unauditable, but I realise that, in practice, it is what most Accounts Offices do. But money matters less than science.

Of course an undetected error may cause an immediate crash, it may cause results to be obviously wrong, it may cause results to be subtly wrong, or it may have no impact on the final result.

#### Keeping up with the CPU

CPU clock speeds in the past twenty years have increased by a factor of around 500. (About 60MHz to about 3GHz.) Their performance in terms of instructions per second has increased by about 10,000, as now one generally has four cores, each capable of multiple instructions per clock cycle, not a single core struggling to maintain one instruction per clock cycle.

The partial answer is to use expensive, fast, cache RAM to store frequently accessed data. Cache is expensive because its SRAM uses multiple transistors per bit (typically six). It is fast, with sub-ns latency, lacking the output buffer of DRAM, and not penalising random access patterns.

But it is power-hungry, space-hungry, and needs to be physically very close to the CPU so that distance does not cause delay. c = 1 in units of feet per ns in vacuum. So a 3GHz signal which needs to travel just two inches and back again will lose a complete cycle. In silicon things are worse.

(Experimentalists claim that c = 0.984 ft/ns.)

56

#### **Caches: the Theory**

The theory of caching is very simple. Put a small amount of fast, expensive memory in a computer, and arrange automatically for that memory to store the data which are accessed frequently. One can then define a cache *hit rate*, that is, the number of memory accesses which go to the cache divided by the total number of memory accesses. This is usually expressed as a percentage & will depend on the code run.

The first paper to describe caches was published in 1965 by Maurice Wilkes (Cambridge). The first commercial computer to use a cache was the IBM 360/85 in 1968.

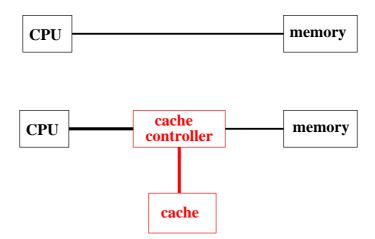

# The Cache Controller

Conceptually this has a simple task:

- Intercept every memory request

- Determine whether cache holds requested data

- If so, read data from cache

- If not, read data from memory *and* place a copy in the cache as it goes past.

However, the second bullet point must be done *very* fast, and this leads to the compromises. A cache controller inevitably makes misses slower than they would have been in the absence of any cache, so to show a net speed-up hits have to be plentiful and fast. A badly designed cache controller can be worse than no cache at all.

58

#### An aside: Hex

A quick lesson in hexadecimal (base-16) arithmetic is due at this point. Computers use base-2, but humans tend not to like reading long base-2 numbers.

Humans also object to converting between base-2 and base-10.

However, getting humans to work in base-16 and convert between base-2 and base-16 is easier.

Hex uses the letters A to F to represent the 'digits' 10 to 15. As  $2^4 = 16$  conversion to and from binary is done trivially using groups of four digits.

#### **Converting to / from Hex**

0101 1101 0010 1010 1111 0001 1100 0011 5 C 2 A F 1 B 3 So

#### $0101\,1101\,0010\,1010\,1111\,0001\,1100\,0011_2$

$= 5C2AF1B3_{16} = 1,546,318,259$

As one hex digit is equivalent to four binary digits, two hex digits are exactly sufficient for one byte.

Hex numbers are often prefixed with '0x' to distinguish them from base ten.

When forced to work in binary, it is usual to group the digits in fours as above, for easy conversion into hex or bytes.

60

# **Our Computer**

For the purposes of considering caches, let us consider a computer with a 1MB address space and a 64KB cache.

An address is therefore 20 bits long, or 5 hex digits, or  $2\frac{1}{2}$  bytes.

Suppose we try to cache individual bytes. Each entry in the cache must store not only the data, but also the address in main memory it was taken from, called the *tag*. That way, the cache controller can look through all the tags and determine whether a particular byte is in the cache or not.

So we have 65536 single byte entries, each with a  $2\frac{1}{2}$  byte tag.

## A Disaster

This is bad on two counts.

#### A waste of space

We have 64KB of cache storing useful data, and 160KB storing tags.

#### A waste of time

We need to scan 65536 tags before we know whether something is in the cache or not. This will take far too long.

62

#### Lines

The solution to the space problem is not to track bytes, but *lines*. Consider a cache which deals in units of 16 bytes.

64KB = 65536 \* 1 byte= 4096 \* 16 bytes

We now need just 4096 tags.

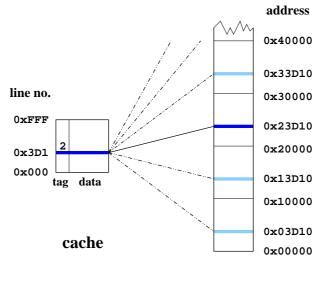

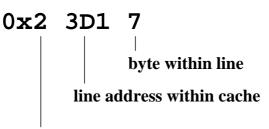

Furthermore, each tag can be shorter. Consider a random address:

0x23D17

This can be read as byte 7 of line 23D1. The cache will either have all of line 23D1 and be able to return byte number 7, or it will have none of it. Lines always start at an address which is a multiple of their length.

# Getting better...

#### A waste of space?

We now have 64KB storing useful data, and 8KB storing tags. Considerably better.

#### A waste of time

Scanning 4096 tags may be a 16-fold improvement, but is still a disaster.

#### **Causing trouble**

Because the cache can store only full lines, if the processor requests a single byte which the cache does not hold, the cache then requests the full line from the memory so that it can keep a copy of the line. Thus the memory might have to supply  $16 \times$  as much data as before!

# **A Further Compromise**

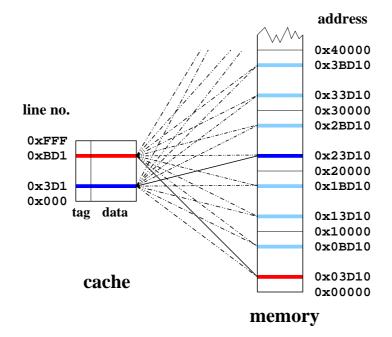

We have 4096 lines, potentially addressable as line 0 to line 0xFFF.

On seeing an address, e.g. 0x23D17, we discard the last 4 bits, and scan all 4096 tags for the number 0x23D1.

Why not always use line number  $0 \times 3D1$  within the cache for storing this bit of memory? The advantage is clear: we need only look at one tag, and see if it holds the line we want,  $0 \times 23D1$ , or one of the other 15 it could hold:  $0 \times 03D1$ ,  $0 \times 13D1$ , etc.

Indeed, the new-style tag need only hold that first hex digit, we know the other digits! This reduces the amount of tag memory to 2KB.

#### **Direct Mapped Caches**

We have just developed a *direct mapped* cache. Each address in memory maps directly to a single location in cache, and each location in cache maps to multiple (here 16) locations in memory.

memory

66

#### Success?

- The overhead for storing tags is 3%. Quite acceptable, and much better than 250%!

- Each 'hit' requires a tag to be looked up, a comparison to be made, and then the data to be fetched. Oh dear. This *tag RAM* had better be very fast.

- Each miss requires a tag to be looked up, a comparison to fail, and then a whole line to be fetched from main memory.

- The 'decoding' of an address into its various parts is instantaneous.

The zero-effort address decoding is an important feature of all cache schemes.

part to compare with tag

### The Consequences of Compromise

At first glance we have done quite well. Any contiguous 64KB region of memory can be held in cache. (As long as it starts on a cache line boundary)

E.g. The 64KB region from 0x23840 to 0x3383F would be held in cache lines 0x384 to 0xFFF then 0x000 to 0x383

Even better, widely separated pieces of memory can be in cache simultaneously. E.g.  $0 \times 15674$  in line  $0 \times 567$  and  $0 \times C4288$  in line  $0 \times 428$ .

However, consider trying to cache the two bytes  $0 \times 03D11$  and  $0 \times 23D19$ . This cannot be done: both map to line  $0 \times 3D1$  within the cache, but one requires the memory area from  $0 \times 03D10$  to be held there, the other the area from  $0 \times 23D10$ .

Repeated accesses to these two bytes would cause cache *thrashing*, as the cache repeatedly caches then throws out the same two pieces of data.

68

#### Associativity

Rather than each line in memory being storable in just one location in cache, why not make it two?

Thus a 2-way associative cache, which requires two tags to be inspected for every access & an extra bit per tag. Can generalise to  $2^n$ -way associativity.

#### **Anti Thrashing Entries**

Anti Thrashing Entries are a cheap way of increasing the effective associativity of a cache for simple cases. One extra cache line, complete with tag, is stored, and it contains the last line expelled from the cache proper.

This line is checked for a 'hit' in parallel with the rest of the cache, and if a hit occurs, it is moved back into the main cache, and the line it replaces is moved into the ATE.

Some caches have several ATEs, rather than just one.

Assume a 16K direct mapped cache with 32 byte lines. a(1,1) comes into cache, pulling a(2-4,1) with it. Then a(1,2) displaces all these, at it must be stored in the same line, as its address modulo 16K is the same. So a(2,1) is not found in cache when it is referenced. With a single ATE, the cache hit rate jumps from 0% to 75%, the same that a 2-way associative cache would have achieved for this algorithm.

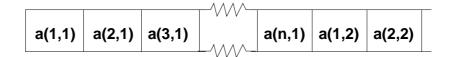

Remember that Fortran and C store arrays in the opposite order in memory. Fortran will have a(1,1), a(2,1), a(3,1)..., whereas C will have a[0][0], a[0][1], a[0][2]...

70

#### **A Hierarchy**

The speed gap between main memory and the CPU core is so great that there are usually multiple levels of cache.

The first level, or *primary cache*, is small (typically 16KB to 128KB), physically attached to the CPU, and runs as fast as possible.

The next level, or *secondary cache*, is larger (typically 256KB to 8MB), slower, and has a higher associativity. There may even be a third level too.

Typical times in clock-cycles to serve a memory request would be:

primary cache 2-4 secondary cache 5-25 main memory 30-300

Cf. functional unit speeds on page 32.

Intel tends to make small, fast caches, compared to RISC workstations which tend to have larger, slower caches.

### Write Back or Write Through?

Should data written by the CPU modify merely the cache if those data are currently held in cache, or modify the memory too? The former, *write back*, can be faster, but the latter, *write through*, is simpler.

With a write through cache, the definitive copy of data is in the main memory. If something other than the CPU (e.g. a disk controller or a second CPU) writes directly to memory, the cache controller must *snoop* this traffic, and, if it also has those data in its cache, update (or invalidate) the cache line too.

Write back caches add two problems. Firstly, anything else reading directly from main memory must have its read intercepted if the cached data for that address differ from the data in main memory.

Secondly, on ejecting an old line from the cache to make room for a new one, if the old line has been modified it must first be written back to memory.

Each cache line therefore has an extra bit in its tag, which records whether the line is modified, or *dirty*.

72

### **Cache Design Decision**

If a write is a miss, should the cache line be filled (as it would for a read)? If the data just written are read again soon afterwards, filling is beneficial, as it is if a write to the same line is about to occur. However, caches which allocate on writes perform badly on randomly scattered writes. Each write of one word is converted into *reading* the cache line from memory, modifying the word written in cache and marking the whole line dirty. When the line needs discarding, the whole line will be written to memory. Thus writing one word has been turned into two lines worth of memory traffic.

What line size should be used? What associativity?

If a cache is n-way associative, which of the n possible lines should be discarded to make way for a new line? A random line? The least recently used? A random line excluding the most recently used?

As should now be clear, not all caches are equal!

The 'random line excluding the most recently used' replacement algorithm (also called pseudo-LRU) is easy to implement. One bit marks the most recently used line of the associative set. True LRU is harder (except for 2-way associative).

### Not All Data are Equal

If the cache controller is closely associated with the CPU, it can distinguish memory requests from the instruction fetcher from those from the load/store units. Thus instructions and data can be cached separately.

This almost universal *Harvard Architecture* prevents poor data access patterns leaving both data and program uncached. However, usually only the first level of cache is split in this fashion.

The instruction cache is usually write-through, whereas the data cache is usually write-back. Write-through caches never contain the 'master' copy of any data, so they can be protected by simple parity bits, and the master copy reloaded on error. Write back caches ought to be protected by some form of ECC, for if they suffer an error, they may have the only copy of the data now corrupted.

The term 'Harvard architecture' comes from an early American computer which used physically separate areas of main memory for storing data and instructions. No modern computer does this.

74

### **Explicit Prefetching**

One spin-off from caching is the possibility of *prefetching*.

Many processors have an instruction which requests that data be moved from main memory to primary cache when it is next convenient.

If such an instruction is issued ahead of some data being required by the CPU core, then the data may have been moved to the primary cache by the time the CPU core actually wants them. If so, much faster access results. If not, it doesn't matter.

If the latency to main memory is 100 clock cycles, the prefetch instruction ideally needs issuing 100 cycles in advance, and many tens of prefetches might be busily fetching simultaneously. Most current processors can handle a couple of simultaneous prefetches...

## **Implicit Prefetching**

Some memory controllers are capable of spotting certain access patterns as a program runs, and prefetching data automatically. Such prefetching is often called *streaming*.

The degree to which patterns can be spotted varies. Unit stride is easy, as is unit stride backwards. Spotting different simultaneous streams is also essential, as a simple dot product:

```

do i=1,n

d=d+a(i)*b(i)

enddo

```

leads to alternate unit-stride accesses for a and b.

IBM's Power3 processor, and Intel's Pentium 4 both spotted simple patterns in this way. Unlike software prefetching, no support from the compiler is required, and no instructions exist to make the code larger and occupy the instruction decoder. However, streaming is less flexible.

76

#### **Clock multiplying**

Today all of the caches are usually found on the CPU die, rather than on external chips. Whilst the CPU is achieving hits on its caches, it is unaffected by the slow speed of the outside world (e.g. main memory).

Thus it makes sense for the CPU internally to use much higher clock-speeds than its external bus. The gap is actually decreasing currently as CPU speeds are levelling off at around 3GHz, whereas external bus speeds are continuing to rise. In former days the gap could be very large, such as the last of the Pentium IIIs which ran at around 1GHz internally, with a 133MHz external bus. In the days when caches were external to the CPU on the motherboard there was very little point in the CPU running faster than its bus. Now it works well provided that the cache hit rate is high (>90%), which will depend on both the cache architecture and the program being run.

In order to reduce power usage, not all of the CPU die uses the same clock frequency. It is common for the last level cache, which is responsible for around half the area of the die, to use clock speeds which are only around a half or a third of those of the CPU core and the primary cache.

## **Thermal Limits to Clock Multiplying**

The rate at which the transistors which make up a CPU switch is controlled by the rate at which carriers get driven out of their gate regions. For a given chip, increasing the electric field, i.e. increasing the voltage, will increase this speed. Until the voltage is so high that the insulation fails.

The heat generated by a CPU contains both a simple ohmic term, proportional to the square of the voltage, and a term from the charging of capacitors through a resistor (modelling the change in state of data lines and transistors). This is proportional to both frequency and the square of the voltage.

Once the CPU gets too hot, thermally excited carriers begin to swamp the intrinsic carriers introduced by the n and p doping. With the low band-gap of silicon, the maximum junction temperature is around 90°C, or just 50°C above the air temperature which most computers can allegedly survive.

Current techniques allow around 120W to be dissipated from a chip with forced air cooling.

Laptops, and the more modern desktops, have power-saving modes in which the clock speed is first dropped, and then a fraction of a second later, the supply voltage also dropped.

78

#### **The Relevance of Theory**

| integer a(*),i,j | int i,j,*a;                              |

|------------------|------------------------------------------|

| j=1              | j=1;                                     |

| do i=1,n         | for (i=0;i <n;i++) td="" {<=""></n;i++)> |

| j=a(j)           | j=a[j];                                  |

| enddo            | }                                        |

This code is mad. Every iteration depends on the previous one, and significant optimisation is impossible.

However, the memory access pattern can be changed dramatically by changing the contents of a. Setting a(i)=i+1 and a(k)=1 will give consecutive accesses repeating over the first k elements, whereas a(i)=i+2, a(k-1)=2 and a(k)=1 will access alternate elements, etc.

One can also try pseudorandom access patterns. They tend to be as bad as large stride access.

#### **Classic caches**

With a 16 element (64 bytes) stride, we see access times of 8.7ns for primary cache, 33ns for secondary, and 202ns for main memory. The cache sizes are clearly 64KB and 2MB.

With a 1 element (4 bytes) stride, the secondary cache and main memory appear to be faster. This is because once a cache line has been fetched from memory, the next 15 accesses will be primary cache hits on the next elements of that line. The average should be (15 \* 8.7 + 202)/16 = 20.7ns, and 21.6ns is observed.

The computer used for this was a 463MHz XP900 (Alpha 21264). It has 64 byte cache lines.

80

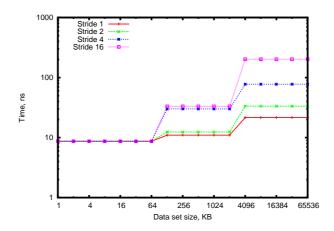

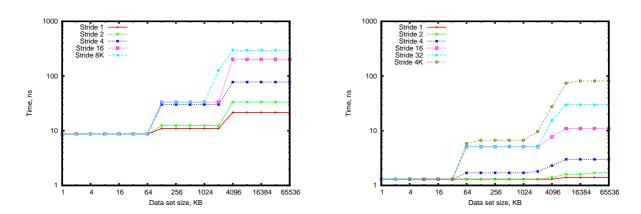

#### **Performance Enhancement** 1000 1000 Stride 1 Stride 2 Stride 4 Stride 1 Stride 2 Stride 4 Stride 16 Stride 32 Stride 16 Stride 32 100 100 Time, ns Time, ns 10 10 16384 1024 4096 16384 65536 1024 4096 65536 16 256 16 256 Data set size, KB Data set size, KB

On the left a 2.4GHz Pentium 4 (launched 2002, RAMBUS memory), and on the right a 2.4GHz Core 2 quad core (launched 2008, DDR3 memory). Both have 64 byte cache lines.

For the Pentium 4, the fast 8KB primary cache is clearly seen, and a 512KB secondary less clearly so. The factor of four difference between the main memory's latency at a 64 byte and 128 byte stride is caused by automatic hardware prefetching into the secondary cache. For strides of up to 64 bytes inclusive, the hardware notices the memory access pattern, even though it is hidden at the software level, and starts fetching data in advance automatically.

For the Core 2 the caches are larger – 32KB and 4MB, and the main memory is a little faster. But six years and three generations of memory technology have changed remarkably little.

#### Matrix Multiplication: $A_{ij} = B_{ik}C_{kj}$

```

do i=1, n

for(i=0;i<n;i++) {</pre>

for(j=0;j<n;j++) {

do j=1, n

t = 0

t = 0;

for (k=0; k<n; k++) {</pre>

do k=1, n

t=t+b(i,k)*c(k,j)

t+=b[i][k]*c[k][j];

enddo

}

a(i,j)=t

a[i][j]=t;

enddo

}

enddo

}

```

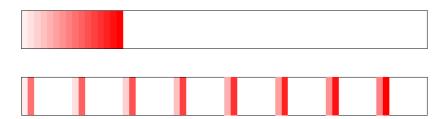

The above Fortran has unit stride access on the array c in the inner loop, but a stride of n doubles on the array b. The C manages unit stride on b and a stride of n doubles on the array c. Neither manages unit stride on both arrays.

Optimising this is not completely trivial, but is very worthwhile.

82

#### **Very Worthwhile**

The above code running on a 2.4GHz Core 2 managed around 500 MFLOPS at a matrix size of 64, dropping to 115 MFLOPS for a matrix size of 1024.

Using an optimised linear algebra library increased the speed for the smaller sizes to around 4,000 MFLOPS, and for the larger sizes to around 8,700 MFLOPS, close to the computer's peak speed of 9,600 MFLOPS.

```

do i=1,nn,2

do j=1,nn

t1=0 ; t2=0

do k=1,nn

t1=t1+b(i,k)*c(k,j)         ! Remember that b(i,k) and

t2=t2+b(i+1,k)*c(k,j)         ! b(i+1,k) are adjacent in memory

enddo

a(i,j)=t1

a(i+1,j)=t2

enddo

enddo

```

This halves the number of passes through b with the large stride, and therefore shows an immediate doubling of speed at n=1024 from 115 MFLOPS to 230 MFLOPS. Much more to be done before one reaches 8,000 MFLOPS though, so don't bother: link with a good BLAS library and use its matrix multiplication routine! (Or use the F90 intrinsic matmul function in this case.) [If trying this at home, note that many Fortran compilers spot simple examples of matrix multiplication and re-arrange the loops themselves. This can cause confusion.]

There are many possibilities to consider for optimising this code. If the matrix size is very small, don't, for it will all fit in L1 cache anyway. For large matrices one can consider transposing the matrix which would otherwise be accessed with the large stride. This is most beneficial if that matrix can then be discarded (or, better, generated in the transposed form). Otherwise one tries to modify the access pattern with tricks such as

# **Memory Access Patterns in Practice**

#### **Matrix Multiplication**

We have just seen that very different speeds of execution can be obtained by different methods of matrix multiplication.

Matrix multiplication is not only quite a common problem, but it is also very useful as an example, as it is easy to understand and reveals most of the issues.

#### **More Matrix Multiplication**

$$A_{ij} = \sum_{k=1,N} B_{ik} C_{kj}$$

So to form the product of two  $N \times N$  square matrices takes  $N^3$  multiplications and  $N^3$  additions. There are no clever techniques for reducing this computational work significantly (save eliminating about  $N^2$  additions, which is of little consequence).

The amount of memory occupied by the matrices scales as  $N^2$ , and is exactly  $24N^2$  bytes assuming all are distinct and double precision.

Most of these examples use N = 2048, so require around 100MB of memory, and will take 16s if run at 1 GFLOPs.

86

#### **Our Computer**

These examples use a 2.4GHz quad core Core2 with 4GB of RAM. Each core can complete two additions and two multiplications per clock cycle, so its theoretical sustained performance is 9.6 GFLOPs.

Measured memory bandwidth for unit stride access over an array of 64MB is 6GB/s, and for access with a stride of 2048 doubles it is 84MB/s (one item every 95ns).

We will also consider something older and simpler, a 2.8GHz Pentium 4 with 3GB of RAM. Theoretical sustained performance is 5.6 GFLOPs, 4.2GB/s and 104ns. Its data in the following slides will be shown in italics in square brackets.

The Core 2 processor used, a Q6600, was first released in 2007. The Pentium 4 used was first released in 2002. The successor to the Core 2, the Nehalem, was first released late in 2008.

### Speeds

```

for (i=0; i<n; i++) {</pre>

do i=1, n

do j=1, n

for(j=0;j<n;j++) {</pre>

t=0

t=0;

do k=1, n

for (k=0; k<n; k++) {</pre>

t=t+b(i,k)*c(k,j)

t+=b[i][k]*c[k][j];

enddo

}

a(i,j)=t

a[i][j]=t;

enddo

}

}

enddo

```

If the inner loop is constrained by the compute power of the processor, it will achieve 9.6 GFLOPs. [5.6 GFLOPS]

If constrained by bandwidth, loading two doubles and performing two FLOPS per iteration, it will achieve 750 MFLOPs. [520 MFLOPS]

If constrained by the large stride access, it will achieve two FLOPs every 95ns, or 21 MFLOPs. [19 MFLOPS]

88

#### **The First Result**

When compiled with gfortran -00 the code achieved 41.6 MFLOPS. [37 MFLOPS]

The code could barely be less optimal – even t was written out to memory, and read in from memory, on each iteration. The processor has done an excellent job with the code to achieve 47ns per iteration of the inner loop. This must be the result of some degree of speculative loading overlapping the expected 95ns latency.

In the mess which follows, one can readily identify the memory location -40 (%rbp) with t, and one can also see two integer multiplies as the offsets of the elements b(i,k) and c(k,j) are calculated.

#### Messy

-192(%rbp), %rbx movq -192(@10r,, -20(%rbp), %esi movl movslq %esi, %rdi -28(%rbp), %esi movl movslq %esi, %r8 -144(%rbp), %rsi movq imulq %r8, %rsi addq %rsi, %rdi movq -184(%rbp), %rsi leaq (%rdi,%rsi), %rsi movsd (%rbx,%rsi,8), %xmm1 movq -272(%rbp), %rbx -28(%rbp), %esi movl movslq %esi, %rdi movl -24(%rbp), %esi movslq %esi, %r8 movq -224(%rbp), %rsi %r8, %rsi imulq addq %rsi, %rdi -264(%rbp), %rsi movq (%rdi,%rsi), %rsi leaq movsd (%rbx,%rsi,8), %xmm0 mulsd %xmm1, %xmm0 movsd -40(%rbp), %xmml addsd %xmm1, %xmm0 movsd %xmm0, -40(%rbp) [ amɔ %ecx, -28(%rbp) sete %b1 movzbl %bl, %ebx addl \$1, -28(%rbp) testl %ebx, %ebx .L22 je

.1.22:

90

#### Faster

When compiled with gfortran -01 the code achieved 118 MFLOPS. The much simpler code produced by the compiler has given the processor greater scope for speculation and simultaneous outstanding memory requests. Don't expect older (or more conservative) processors to be this smart – on an ancient Pentium 4 the speed improved from 37.5 MFLOPS to 37.7 MFLOPS.

Notice that t is now maintained in a register, %xmm0, and not written out to memory on each iteration. The integer multiplications of the previous code have all disappeared, one by conversion into a Shift Arithmetic Left Quadbyte of 11 (i.e. multiply by 2048, or 2^11).

.L10: movslq %eax, %rdx %rdx, %rcx movq \$11, %rcx salq -2049(%rcx,%r8), %rcx leaq %rdi, %rdx addq movsd 0(%rbp,%rcx,8), %xmml mulsd (%rbx,%rdx,8), %xmm1 %xmm1, %xmm0 addsd addl \$1, %eax -1(%rax), %edx leal cmpl %esi, %edx jne .L10

### **Unrolling: not faster**

```

do i=1,nn

do j=1,nn

t=0

do k=1,nn,2

t=t+b(i,k)*c(k,j)+b(i,k+1)*c(k+1,j)

enddo

a(i,j)=t

enddo

enddo

```

This 'optimisation' reduces the overhead of testing the loop exit condition, and little else. The memory access pattern is unchanged, and the speed is also pretty much unchanged – up by about 4%.

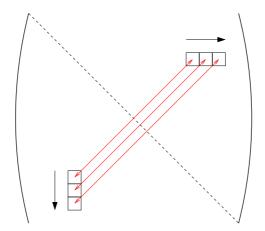

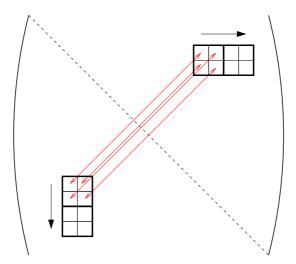

#### **Memory Access Pattern**

### **Blocking: Faster**

```

do i=1,nn,2

do j=1,nn

t1=0

t2=0

do k=1,nn

t1=t1+b(i,k)*c(k,j)

t2=t2+b(i+1,k)*c(k,j)

enddo

a(i,j)=t1

a(i+1,j)=t2

enddo

enddo

```

```

This has changed the memory access pattern on the array b. Rather than the pessimal order b(1,1) b(1,2) b(1,3) b(1,4) ... b(1,n) b(2,1) b(2,2) we now have b(1,1) b(2,1) b(1,2) b(2,2) .... b(1,n) b(2,n) b(3,1) b(4,1) Every other item is fetched almost for free, because its immediate neighbour has just been fetched. The number of iterations within this inner loop is the same, but the loop is now

```

executed half as many times.

94

#### Yes, Faster

We would predict a speedup of about a factor of two, and that is indeed seen. Now the Core 2 reaches 203 MFLOPS (up from 118 MFLOPS), and the Pentium 4 71 MFLOPS (up from 38 MFLOPS).

Surprisingly changing the blocking factor from 2 to 4 (i.e. four elements calculated in the inner loop) did not impress the Core 2. It improved to just 224 MFLOPS (+10%). The Pentium 4, which had been playing fewer clever tricks in its memory controller, was much happier to see the blocking factor raised to 4, now achieving 113 MFLOPS (+59%).

#### More, more more!

With nb=1 this code is mostly equivalent to our original naïve code. Only less readable, potentially buggier, more awkward for the compiler, and a(i, j) is now unlikely to be cached in a register. With nb=1 the Core 2 achieves 74 MFLOPS, and the Pentium 4 33 MFLOPS. But with nb=64 the Core 2 achieves 530 MFLOPS, and the Pentium 4 320 MFLOPS – their best scores so far.

96

#### Better, better, better

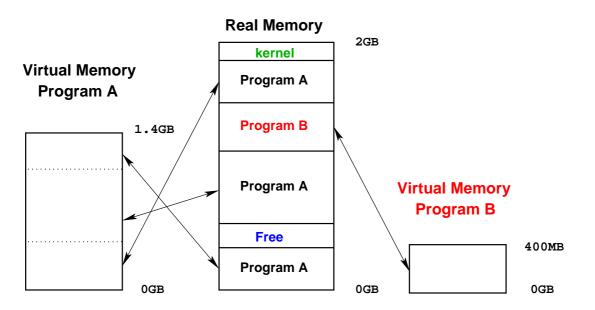

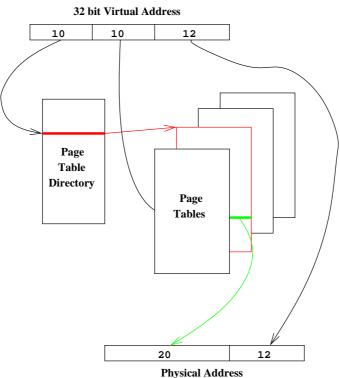

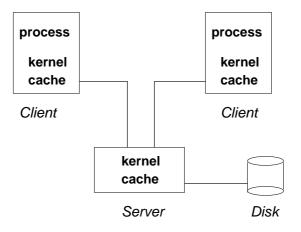

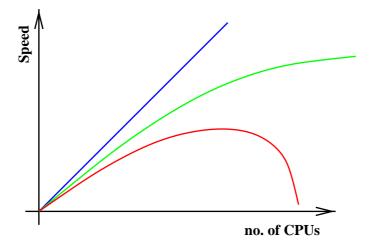

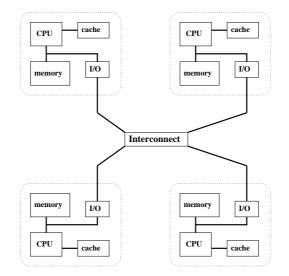

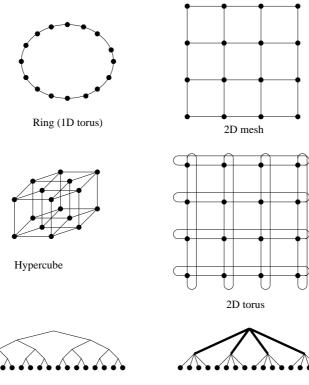

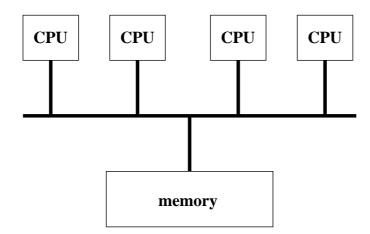

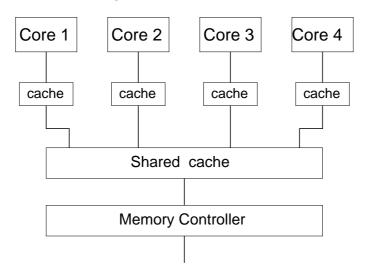

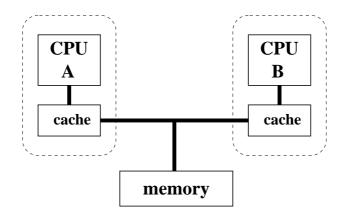

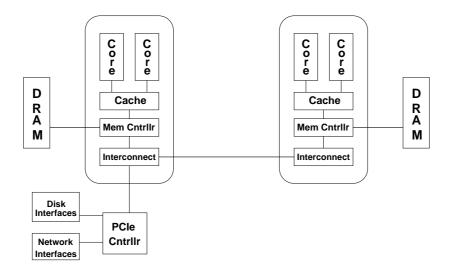

Fewer loads and stores on a(i, j), and the Core 2 likes this, getting 707 MFLOPS. The Pentium 4 now manages 421 MFLOPS. Again this is trivially extended to a step of four in the k loop, which achieves 750 MFLOPS [448 MFLOPS]